There’s an on-going translation effort (into English) at:

Eu já contei um pedacinho minúsculo dessa história em uma postagem do meu blog (em inglês) em:

http://mamedev.emulab.it/fsanches/2015/11/18/a-pleasant-visit-to-the-university/

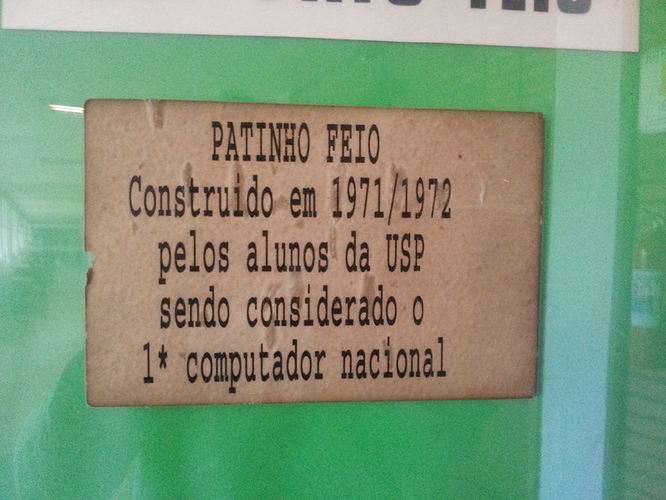

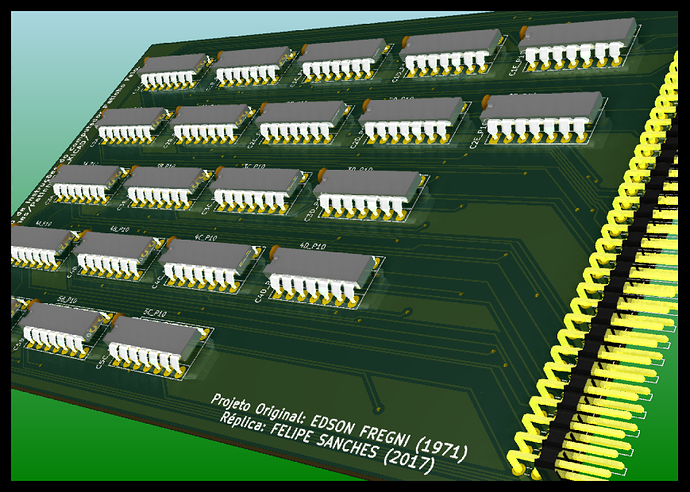

Mas aqui eu vou entrar em mais detalhes e tentar contar tudo o que aconteceu até agora e, possivelmente, as atualizações dos próximos passos desse trabalho de resgate histórico do computador Patinho Feio, que foi projetado na USP em 1971.

Em novembro de 2015 eu estava muito interessado em escanear gabinetes de arcades e consoles de video-game e, por causa disso, fui à USP tentar falar com alguém do LSI ou da Caverna Digital, em busca de um scanner 3D. Não achei a professora Roseli de Deus Lopes (do LSI) nessa visita, mas acabei me encontrando com o professor João José Neto.

Nessa conversa com o professor JJNeto, comentei que já tenho trabalhado há alguns anos voluntariamente em iniciativas de preservação histórica de computadores e video-games (e, na realidade, qualquer equipamento digital) por meio de técnicas de emulação e que, com esse objetivo, tenho contribuído com a implementação de emuladores para o Projeto MAME.

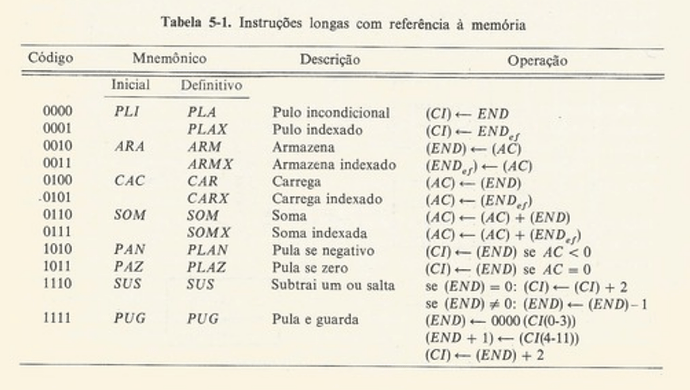

Cheguei a mostrar ao professor alguns dos meus drivers no MAME e ele, em retribuição, colocou em minhas mãos um documento de 1977 chamado “Montador do ‘Patinho Feio’”. Trata-se de um manual de uso do software montador (assembler) para a linguagem de máquina da CPU do computador Patinho Feio. Como supostamente não havia conhecimento da existência de outra cópia desse documento, eu fiquei bastante preocupado, pois era um documento de quase 40 anos que tinha sido mantido em ótimas condições de preservação até então. E agora essa raridade estava sendo colocada em minhas mãos estabanadas…

Eu fiquei apavorado! Corri pra casa com todo o cuidado para proteger o documento e, de imediato, dei início ao processo de digitalização assim que cheguei em casa. Como não cabia no meu scanner (as folhas eram um pouquinho maiores que o tamanho padrão A4) eu simplesmente tirei fotos de cada uma das páginas usando o meu celular. Guardei todas as fotos em alta resolução em um repositório no GitHub, e depois fiz um pequeno script para reduzir e comprimir as páginas e em seguida concatená-las em um PDF de qualidade e tamanho razoáveis. O PDF final foi publicado no Internet Archive e pode ser visto aqui:

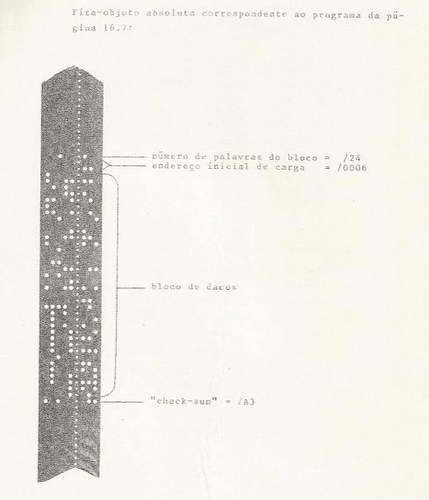

Em seguida, estudei o documento inteiro e notei que com a informação disponível alí seria possível implementar um emulador para a CPU do Patinho Feio. Para testar o emulador, entretanto, eu precisaria ter em mãos programas para esse computador. E até então a única coisa que eu tinha acesso era um pequeno “Hello World” cujo código de máquina era legível na fotografia de um pequeno trecho de fita perfurada que aparecia numa imagem do próprio documento.

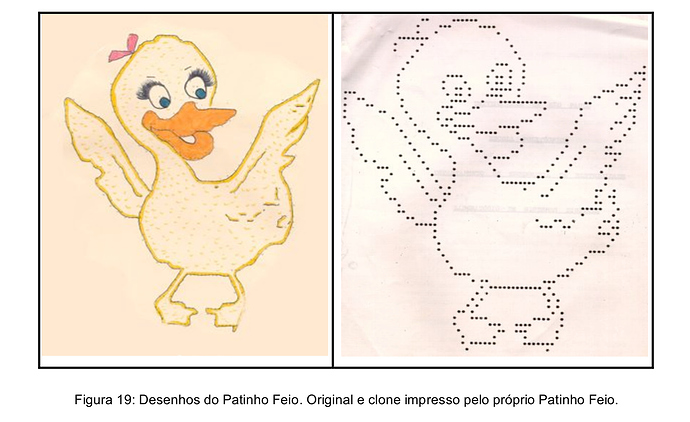

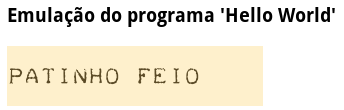

Transcrevi manualmente cada um dos bytes desta fita da imagem, gerando um arquivo binário que pudesse ser carregado no meu emulador e, em seguida, usei esse código para depurar a minha implementação. Com isso, consegui fazer o programinha funcionar no emulador e ver sendo exibidos na tela os caracteres que originalmente eram enviados à teletype - uma máquina de escrever com interface serial para comunicação com o computador. Pausadamente, foram sendo enviados um a um os caracteres: P - A - T - I - N - H - O - [espaço] - F - E - I - O seguidos de um comando de linefeed (alimentação de uma linha de papel) e depois um carriage return (retorno do carro de impressão).

Usando uma tecnologia chamada emscripten, fiz uma compilação deste driver do MAME para javascript, o que permite rodar o emulador direto no browser. Na época eu montei uma página web para hospedar essa demonstração. Veja aqui:

http://felipesanches.github.io/emuladores/patinho.html

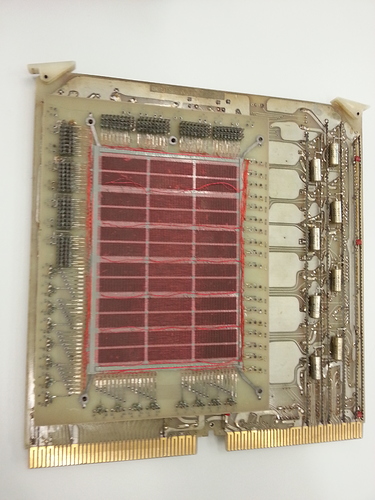

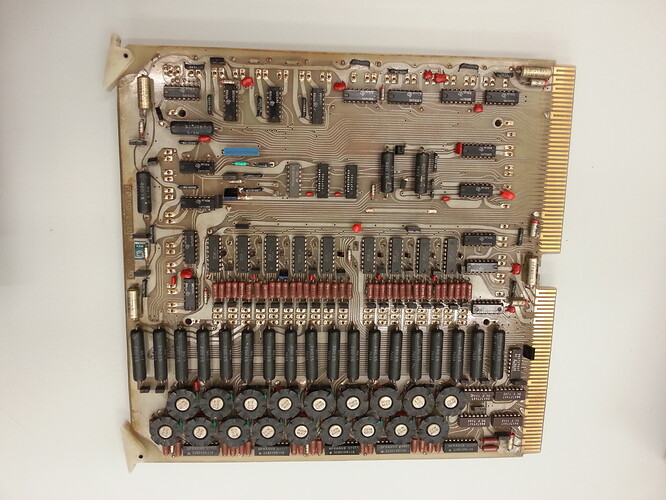

Fui mais uma vez à Poli-USP algum tempo depois e, junto com o Armando Neto (amigo nosso aqui do Fiozeira!), tiramos algumas fotografias do computador de verdade, que está hoje em dia exposto no prédio da administração / diretoria da Escola Politécnica.

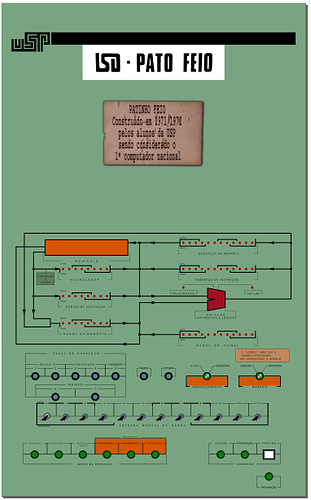

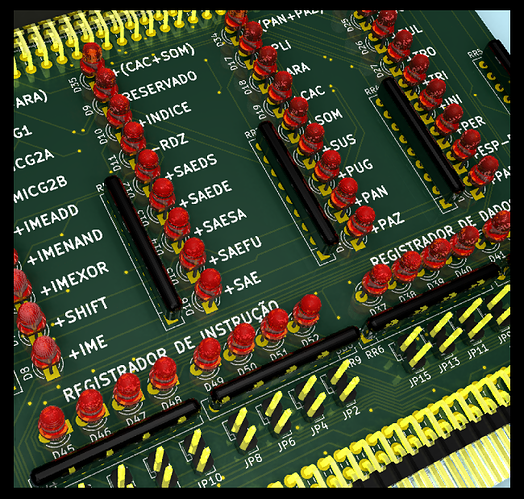

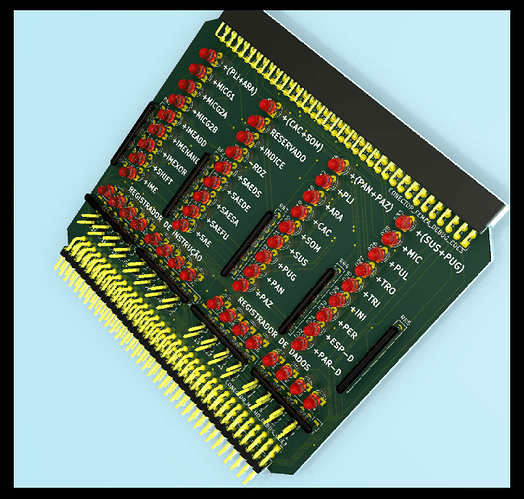

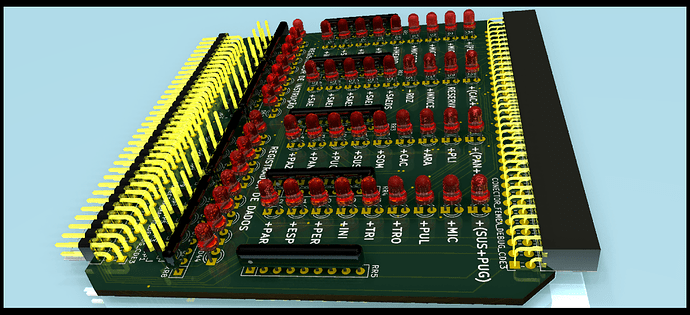

Com base nessas fotografias eu redesenhei o painel completo usando o programa Inkscape (um software livre para desenhos vetoriais) e, com o vetor da arte do painel em mãos, dei início à construção de uma réplica do Patinho Feio, encomendando o corte a laser e a impressão de um adesivo com a arte em uma gráfica rápida perto da minha casa.

Na imagem abaixo se vê a vetorização da arte do painel frontal:

O vetor correspondente está disponível aqui.

Comprei LEDs vermelhos, botões e chaves na Santa Ifigênia e coloquei no vetor de corte a laser as furações adequadas:

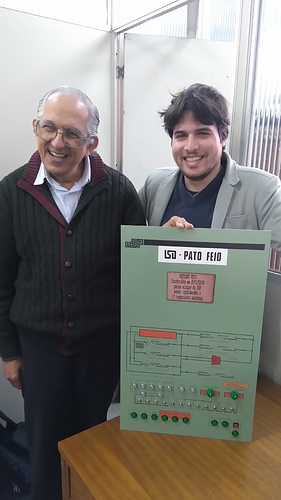

Depois que terminei de construir a parte física do painel, levei para o professor JJNeto ver e parece que ele gostou:

Depois adicionei uma moldura de quadro preta e hoje em dia o painel tem esse aspecto visual:

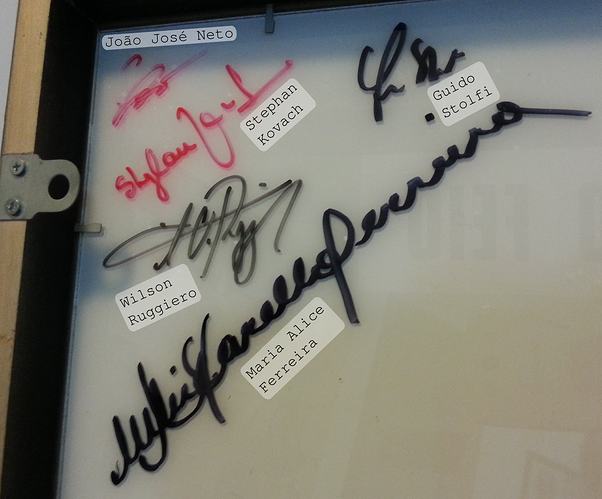

Estou gradualmente coletando também autógrafos no lado de trás do painel, de professores que, na década de 70, participaram do desenvolvimento do projeto na USP:

Em resposta à minha postagem original no blog sobre a descoberta do manual do montador, um amigo fez o seguinte comentário:

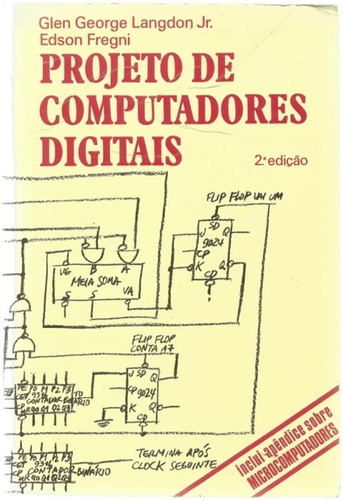

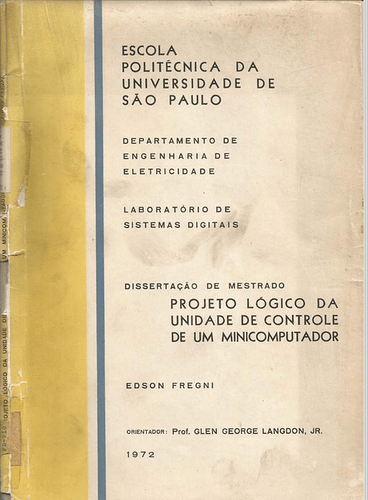

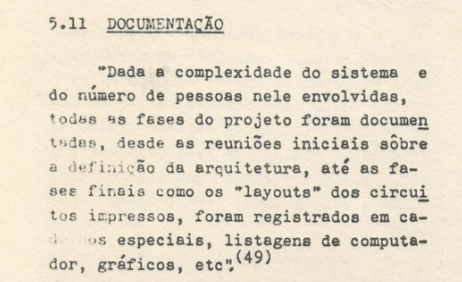

Não consigo me lembrar se foi ou não por conta disso que parti para o próximo passo nesse projeto. Mas o fato é que eu fui até a biblioteca e, com a ajuda do prof JJNeto que usou a carteirinha dele para empréstimo de livros pois a minha já não é mais válida desde quando saí da USP, retiramos algumas teses relativas ao tema. Ao longo dos meses seguintes eu fui aos poucos escaneando cada uma das teses de mestrado e de doutorado que tinham alguma ligação com o projeto do Patinho Feio. São cerca de 15 documentos (não lembro de cabeça a conta exata). Cada um deles teve suas páginas escaneadas em alta resolução e publicadas em repositórios individuais na minha conta do GitHub, enquanto os PDFs finais foram agrupados inicialmente em um repositório central aqui:

Estou agora subindo os PDFs também no Internet Archive em:

https://archive.org/search.php?query=subject%3A"patinho+feio"

Bem… acho que já tem MUITA informação nessa postagem. Divirtam-se digerindo tudo isso! Tenho muito mais pra falar, mas fica guardado para postagens futuras. Minha meta atual é terminar a instalação da fiação no painel-miniatura e portar o código de emulação do MAME para rodar em um Arduino controlando as luzes e a leitura das chaves. Mais uma vez, conforme eu for avançando nesse projeto irei postar mais mensagens aqui.

Happy Hacking!

Felipe “Juca” Sanches